Introduction

We are taught how to conduct basic arithmetic operations in signed-magnitude representation from an early age. When the processes are carried out by hardware, this knowledge is extremely useful.

However, in order to carry out the operation and produce a correct result, the designer must be completely familiar with the sequence of actions that must be followed. An algorithm is a solution to a problem that is stated by a finite number of well-defined procedural steps.

When negative values are in signed-2's complement representation, an algorithm for adding two fixed-point binary numbers has been proposed. This is a simple algorithm to build because it only requires a parallel binary adder.

When negative numbers are represented in signed-magnitude form, the process becomes slightly more involved, requiring circuits to add and subtract as well as compare the signs and magnitudes of the numbers.

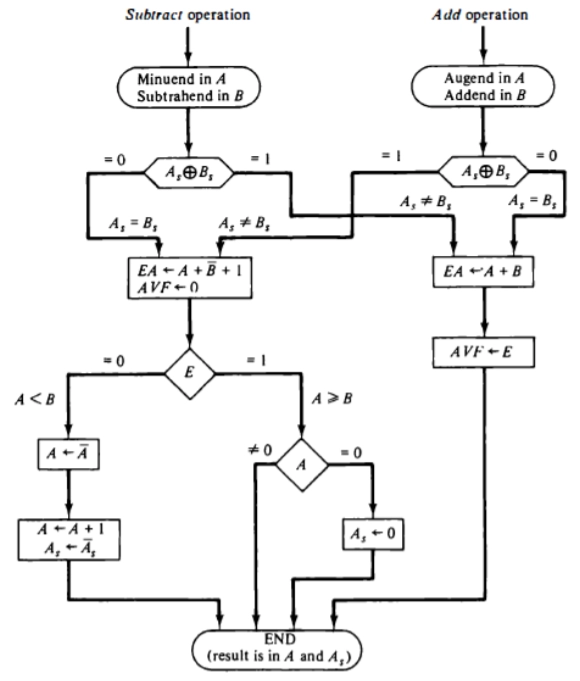

An algorithm usually consists of a series of procedural stages, each of which is dependent on the results of previous phases. A flowchart is a useful tool for presenting algorithms. Rectangular boxes represent the computational steps in the flowchart.

Inside diamond-shaped boxes, two or more alternate paths emerge, the decision stages are shown.

This article develops the various arithmetic algorithms and shows the procedure for implementing them with digital hardware. We consider addition and subtraction for the following types of data:

- Fixed-point binary data in signed-magnitude representation

- Fixed-point binary data in signed-2's complement representation

Computers employ a signed-magnitude approach to implement floating-point operations. Most computers utilise signed-2's complement approach for arithmetic operations on integers. The leftmost bit in the number is utilised to represent the sign in this technique; 0 denotes a positive integer, while 1 indicates a negative integer. The magnitude of the number was supported by the remaining bits in the number.

Also see, Difference Between Jfet and Mosfet

Addition and Subtraction with Signed Magnitude Data

Addition Algorithm

The addition algorithm specifies that:

- If the signs of P and Q are the same, add both the magnitudes and put the sign of P to the result, as shown in the table below.

- Compare both the magnitudes and subtract the small number from the greater number when the signs of P and Q disagree.

- In cases where P > Q, the output signs must be equal to P, or the complement of P's sign in cases where P < Q.

- Subtract Q from P and change the sign of the output to positive when the two magnitudes are equal.

Subtraction Algorithm

The subtraction algorithm states that:

- When the signs of P and Q differ, the subtraction method says to add both the magnitudes and put the sign of P to the result.

- Compare both the magnitudes and subtract the smaller number from the greater number when the signs of P and Q are the same.

- In cases where P > Q, the output signs must be equal to P, or the complement of P's sign in cases where P < Q.

- Subtract Q from P and change the sign of the output to positive when the two magnitudes are equal.

| Operations | Addition of Magnitudes | Subtraction of Magnitudes | ||

|---|---|---|---|---|

| P>Q | P<Q | P=Q | ||

| (+P) + (+Q) | +(P+Q) | |||

| (+P) + (-Q) | +(P-Q) | -(Q-P) | +(P-Q) | |

| (-P) + (+Q) | -(P-Q) | +(Q-P) | +(P-Q) | |

| (-P) + (-Q) | -(P+Q) | |||

| (+P) - (+Q) | +(P-Q) | -(Q-P) | +(P-Q) | |

| (+P) - (-Q) | +(P+Q) | |||

| (-P) - (+Q) | -(P+Q) | |||

| (-P) - (-Q) | -(P-Q) | +(Q-P) | +(P-Q) | |

Flowchart

Flowchart for addition and subtraction

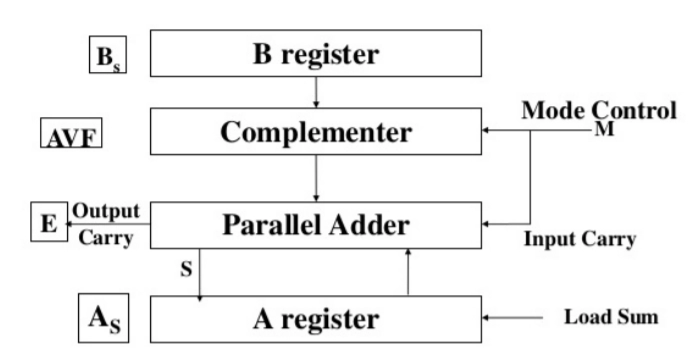

Hardware Implementation

Hardware for signed-magnitude addition and subtraction

Example 1

Let's add two values, +3 and +2, using the signed magnitude representation.

Solution

We represent the given operands as shown below:

+3 = 0 0112

+2 = 0 0102

From the flowchart, we follow that As xor Bs = 0. This implies that As = Bs

Also, according to the table,

| Operations | Addition of Magnitudes | Subtraction of Magnitudes | ||

|---|---|---|---|---|

| (+P) + (+Q) | +(P+Q) | |||

So we do the addition of the magnitude of both operands.

Mag(+3) + Mag(+2) = 0112 + 0102 = 1012 = Mag(5)

Now the sign of the result will be that of As

Therefore, +3 + (+2) = 0 1012 = +5

Example 2

Let's subtract two values, +3 and +2, using the signed magnitude representation.

Solution

We represent the given operands as shown below:

+3 = 0 0112

+2 = 0 0102

From the flowchart, we follow that As xor Bs = 0. This implies that As = Bs

Also according to the table,

| Operations | Addition of Magnitudes | Subtraction of Magnitudes | ||

|---|---|---|---|---|

| P>Q | P<Q | P=Q | ||

| (+P) - (+Q) | +(P-Q) | -(Q-P) | +(P-Q) | |

Since the magnitude of P > Q,

We get results by +(P-Q).

Mag(Result) = 011 + (010)’ + 1 = 011 + 101 + 1 = (001)

SignBit(Result) = 0

Therefore, +3 - (+2) = +(+3-2) = +1

Also see, What Is a Motherboard and what is middleware