Introduction

A counter is a unique type of sequential circuit or device used to store the number of times a specific event or procedure has occurred, frequently about a clock signal. We use counters in digital electronics to count how many times a particular event happened in the circuit. For example, the UP counter increases the count for every rising edge of the clock. We can also design counters with the help of flip-flops. Not only can a counter count, but it can also follow a specific sequence depending on our design, such as any random sequence 0,1,3,2...

We have two types of category of counters -

- Asynchronous/Ripple counters

- Synchronous counters

Asynchronous Counter

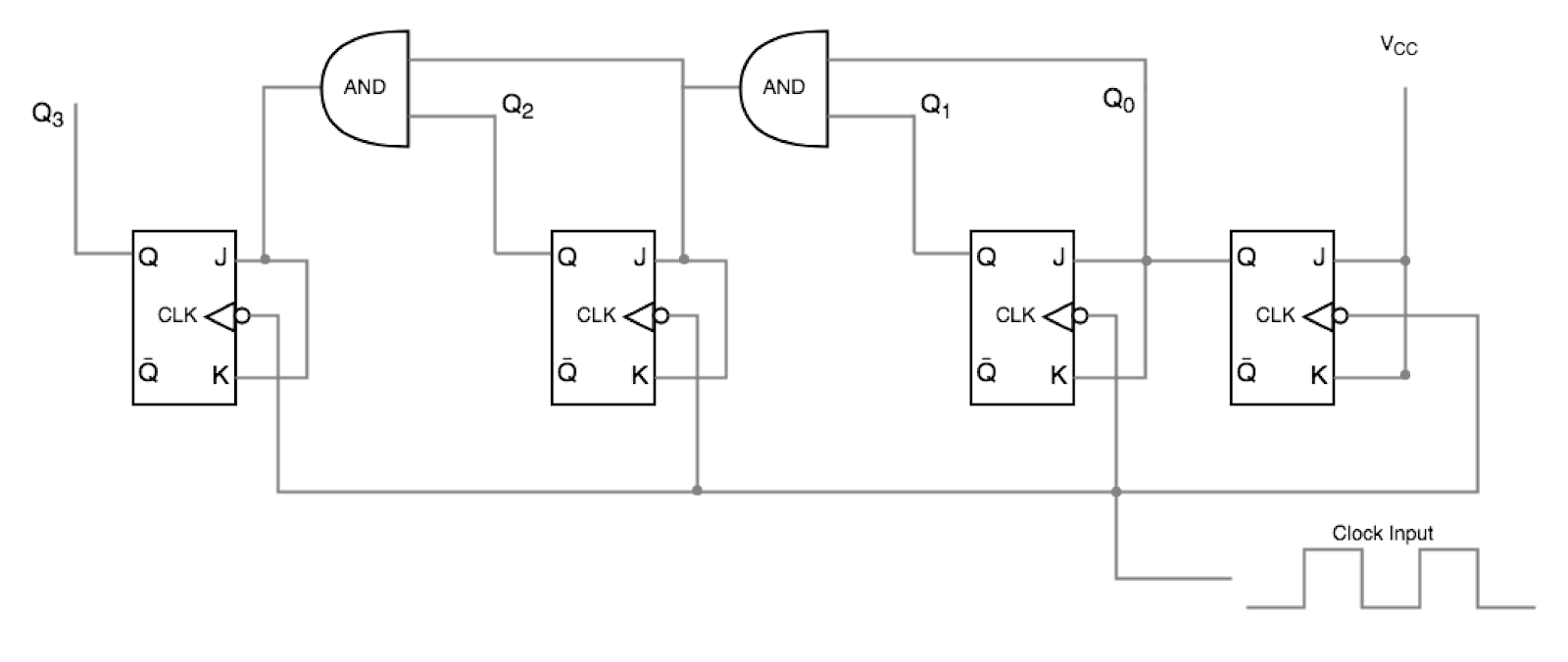

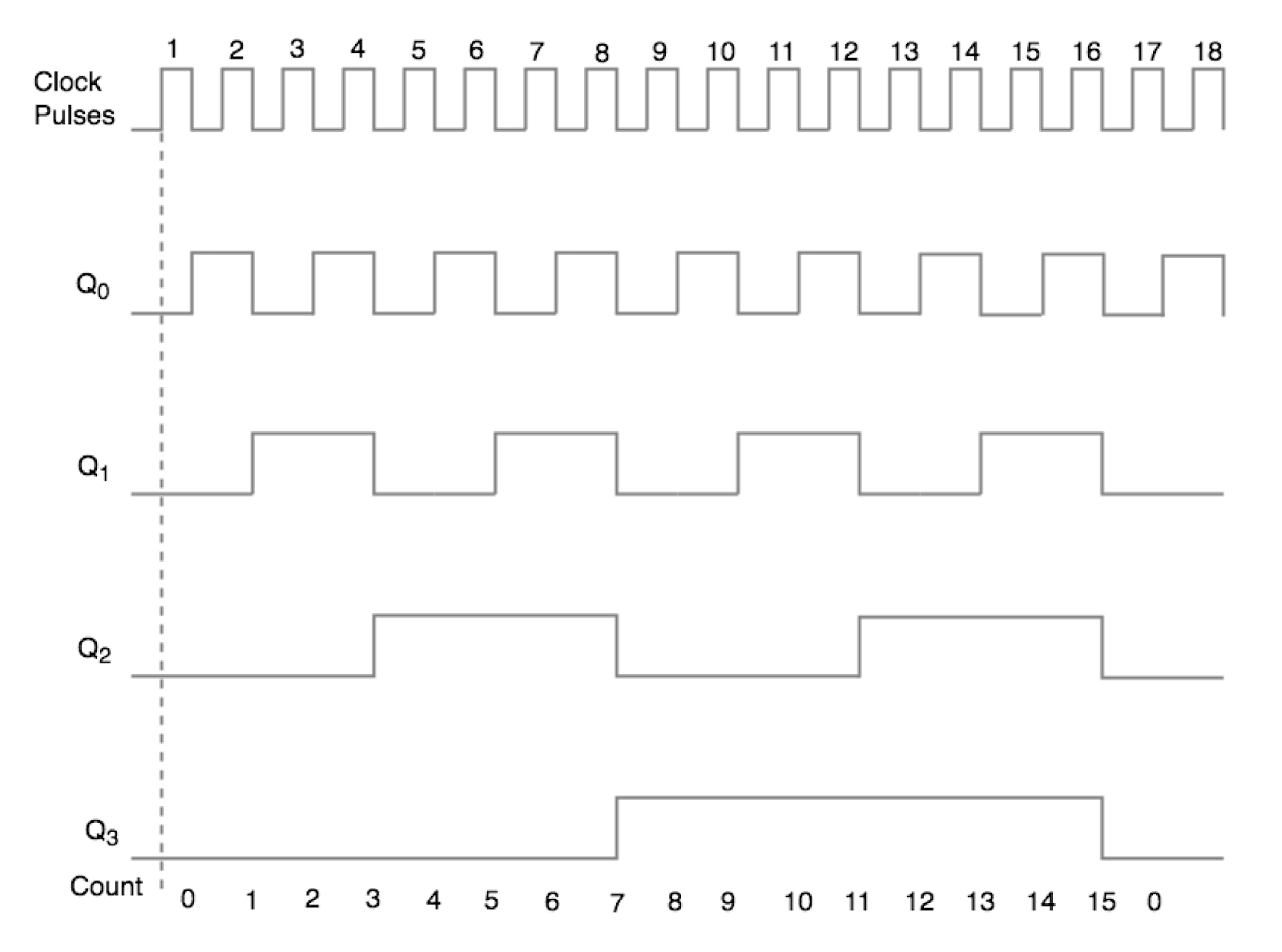

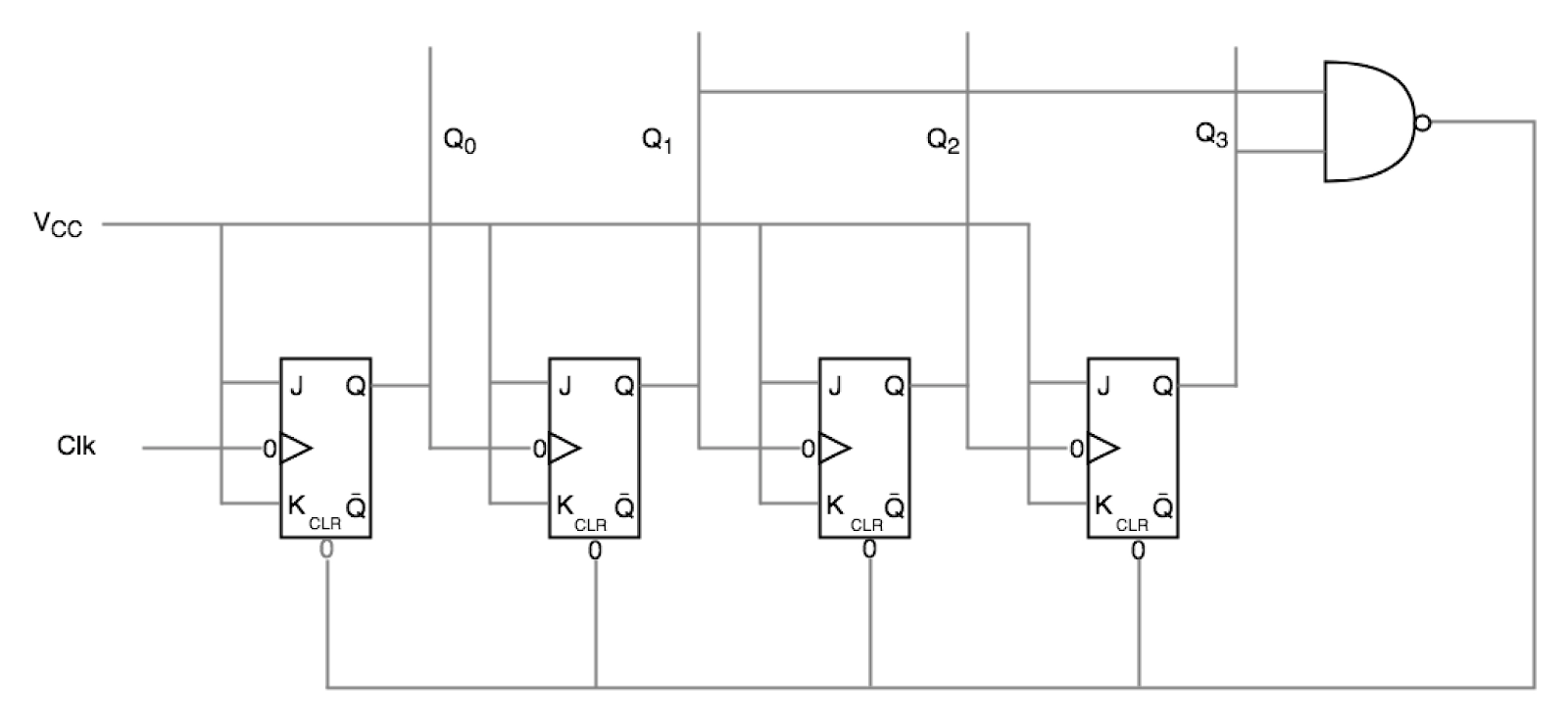

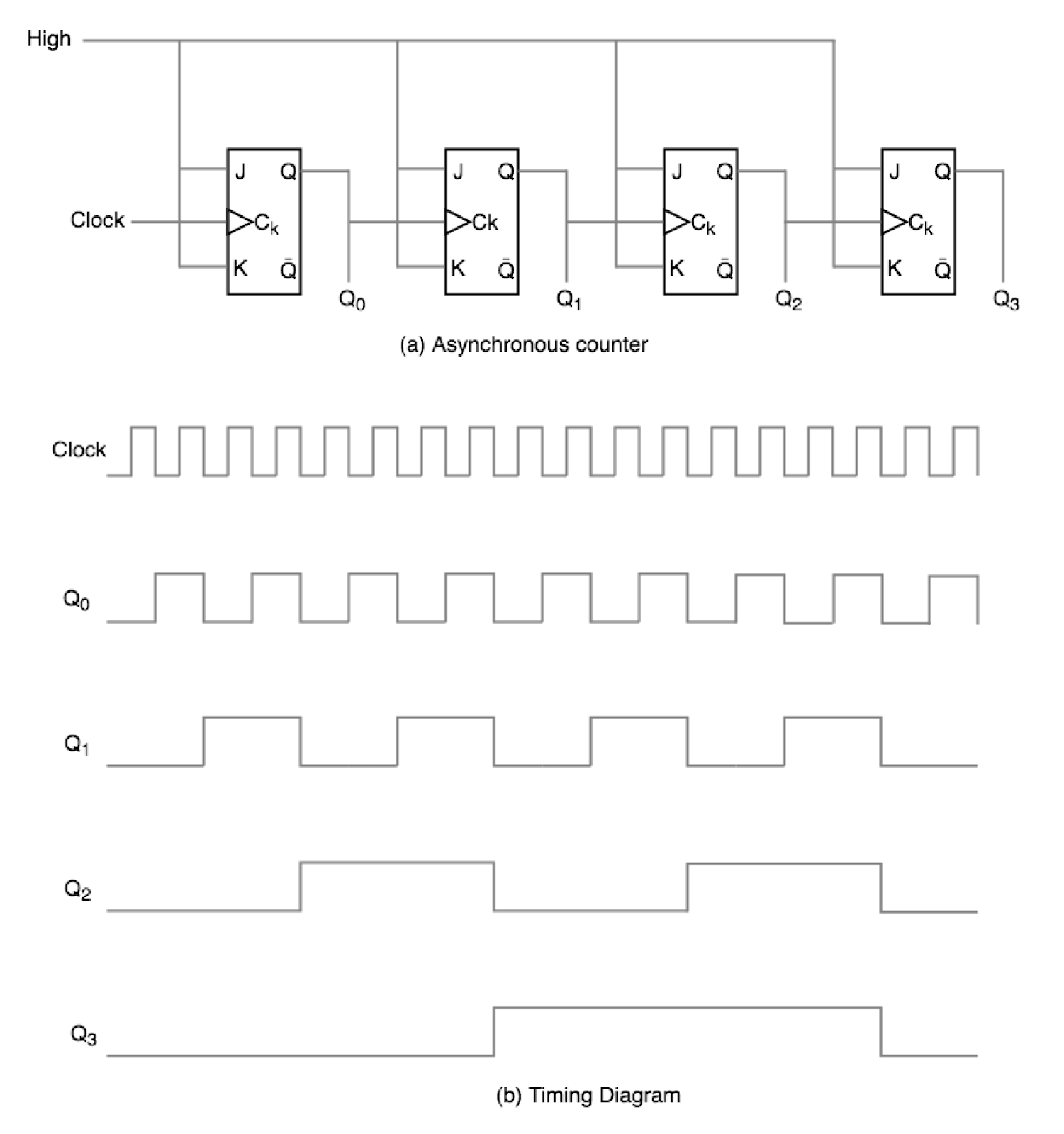

The asynchronous counter is also called the ripple counter. We use two T flip flops or J K flip flops by setting both of the inputs to 1 permanently. In an asynchronous counter, there is no universal clock. The clock drives only the first flip flop of the asynchronous counter, and the rest are driven by the output of the previous flip flop. We will understand this with the help of the following diagram-

As seen in the timing diagram, as soon as the clock pulse rising edge is encountered, Q0 changes. Furthermore, when the rising edge of Q0 is encountered, Q1 changes because Q0 is the clock pulse for Q1. Because ripples are created in this manner by Q0, Q1, Q2, Q3, it is also known as the RIPPLE counter.

Operation for Asynchronous Counter

For now, we will see the operation for only two flip flips with output Q0 Q1.

Condition 1: Both flip flops are in rest condition.

Operation: The output of both the flip flops will be 0.

Condition 2: While the first negative clock edge occurs.

Operation: The output of the first flop will change from 0 to 1 as it will toggle. Then the clock input of the next flip flop will take the output of the first flip flop. Because it is the negative edge-triggered flip flop, this input does not affect the output state of the second flip flop.

Condition 3: During the occurrence of the second negative clock edge.

Operation: Now, the first flip will toggle again, and its output will change from 1 to 0. The second flip flop will use this output as a negative edge clock. Because it is the negative edge-triggered flip flop, this input will affect the output state of the second flip flop.

Condition 4: During the occurrence of third negative clock edge.

Operation: Now, the first flip will toggle again, and its output will change from 0 to 1. The second flip flop will use this output as a positive edge clock. Because it is the negative edge-triggered flip flop, this input will not affect the output state of the second flip flop.

Condition 5: During the occurrence of the fourth negative clock edge.

Operation: Now, the first flip will toggle again, and its output will change from 1 to 0. The second flip flop will use this output as a negative edge clock. Because it is the negative edge-triggered flip flop, this input will affect the output state of the second flip flop.