Introduction

A JK flip-flop is a sequential bi-state single-bit memory device named after its inventor Jack Kilby. The JK flip-flop is a gated SR flip flop with the addition of a clock input circuitry that prevents the invalid or illegal output condition that can occur when both inputs R and S are equal to logic level "1".

Flip flops are of the following types:

- SR Flip Flop

- JK Flip Flop

- D Flip Flop

- T Flip Flop

We have discussed other flip flops in our previous blogs. In this blog, we will dive deep into the JK flip flop.

What is a JK flip flop?

A JK flip flop has very similar characteristics to an SR flip flop. The only difference between them is that the undefined condition for an SR flip-flop, i.e., Rn=Sn= 1 condition, is also included in this case. Inputs J and K behave like inputs S and R to set and reset the flip flop.

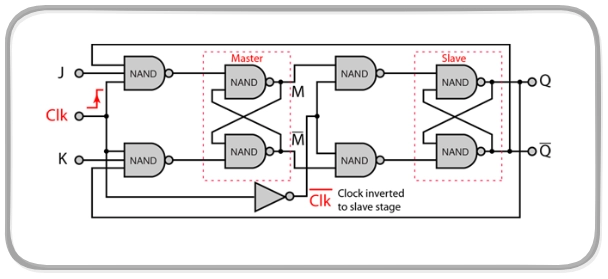

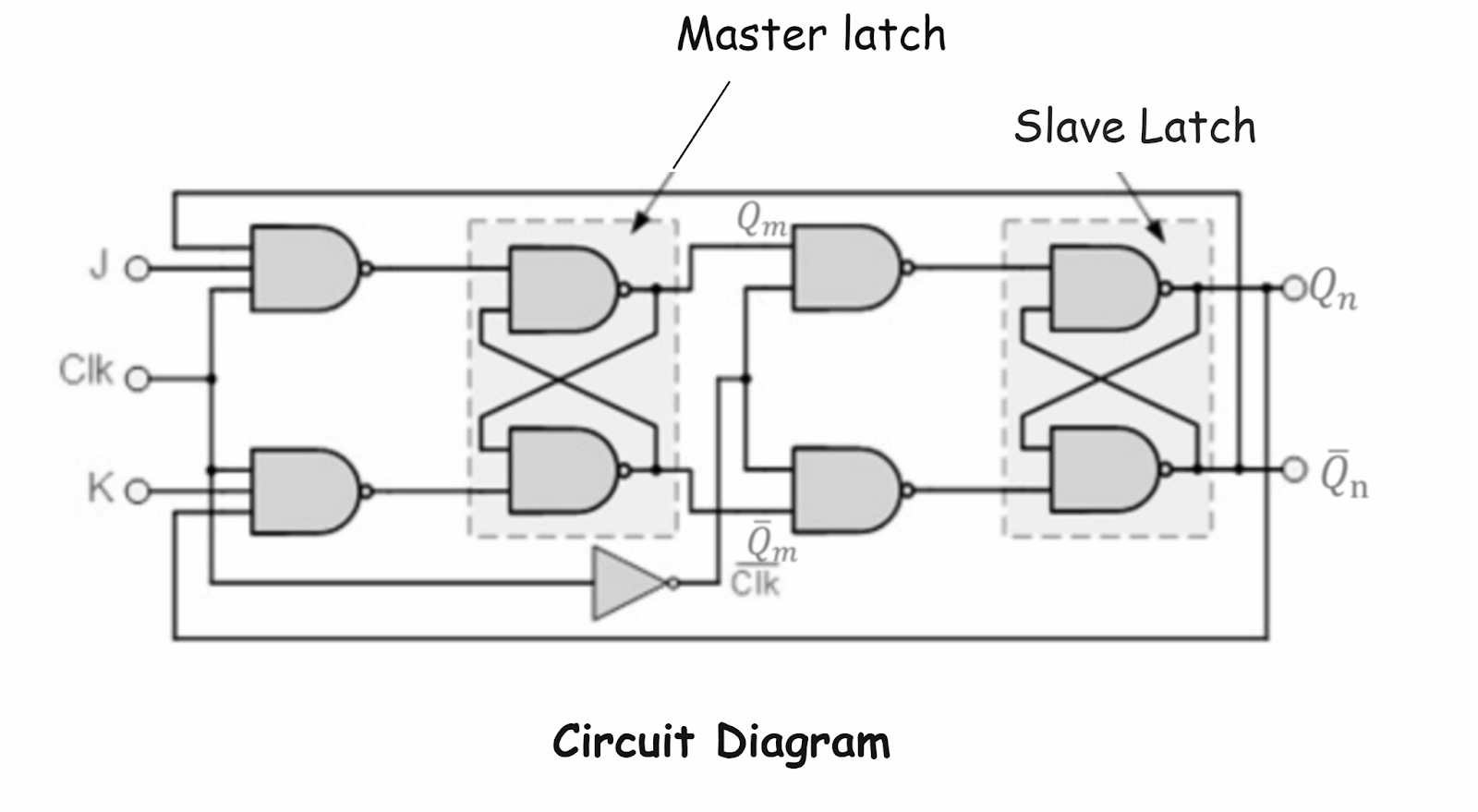

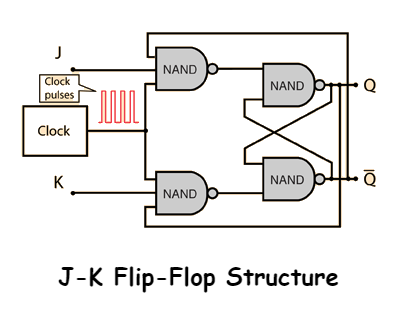

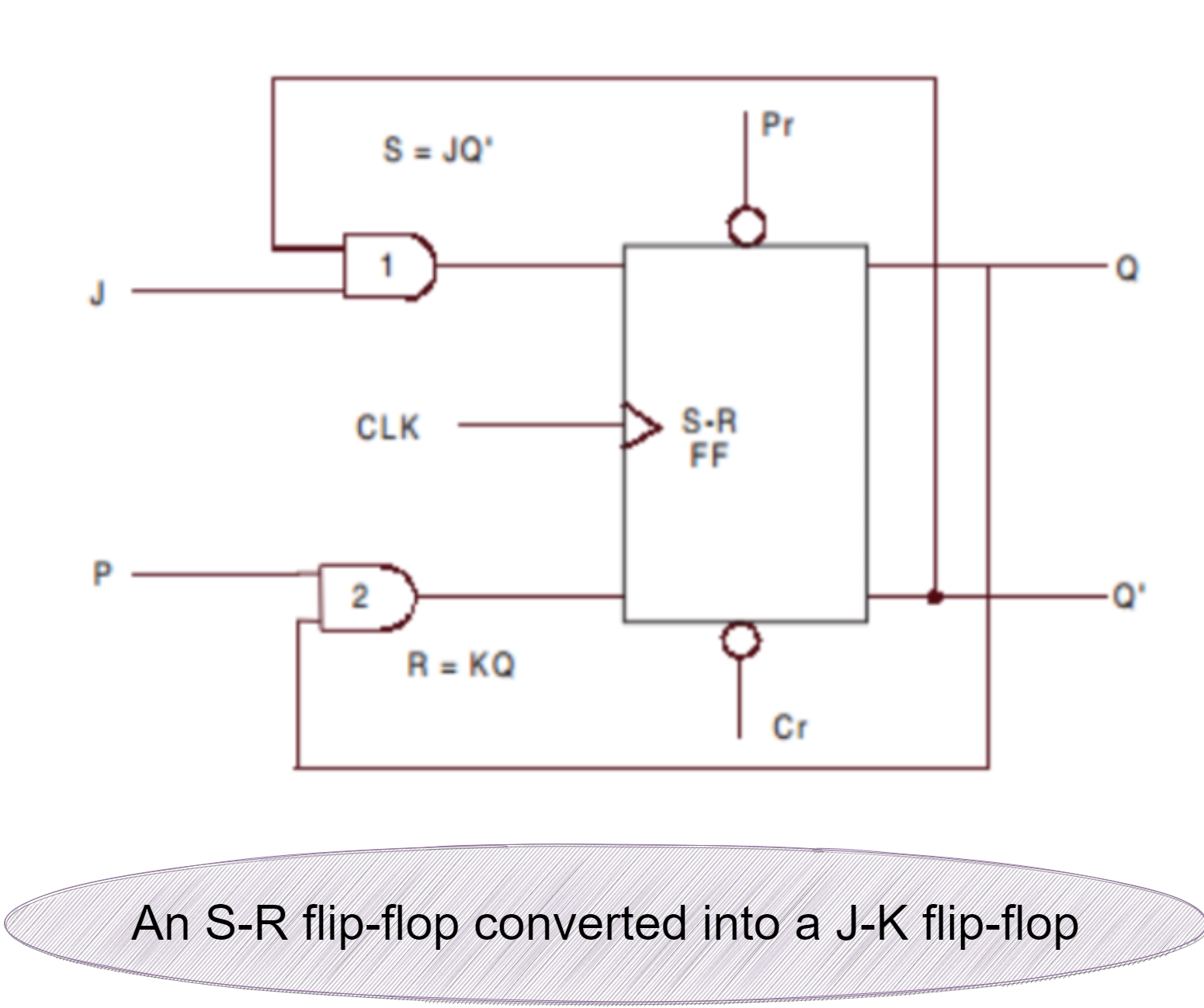

When J = K = 1, the flip flop is in a toggle state, which means the output switches to its complementary state every time a clock passes. The data inputs are J and K, which are ANDed with Q' and Q respectively to obtain the inputs for S and R. A J-K flip flop thus obtained is shown in Figure below.

The only difference between SR and JK flip-flop is that when both inputs of SR flip flop is set to value 1, the circuit produces an output as the invalid states, but in the case of JK flip flop, there are no invalid states even if both 'J' and 'K' flip flops are set to value 1.

JK flip-flop Truth table

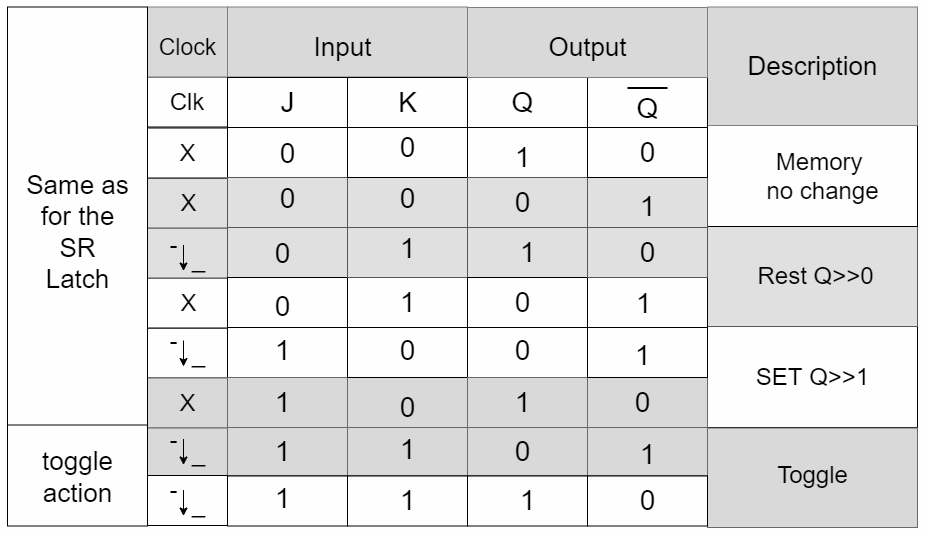

Case 1: When the clock is applied and J = 0, whatever the value of Q'n (0 or 1), the output of NAND gate 1 is 1. Similarly, when K = 0, whatever the value of Qn (0 or 1), the output of gate 2 is also 1. Therefore, when J = 0 and K = 0, the inputs to the basic flip-flop are S = 1 and R = 1. This condition forces the flip-flop to remain in the same state.

Case 2: When the clock is applied and J = 0 and K = 1 & the previous state of the flip-flop is reset (i.e., Qn = 0 and Q'n = 1), then S = 1 and R = 1. Since S = 1 and R = 1, the basic flip-flop does not alter the state and remains in the reset state. But if the flip-flop is in set condition (i.e., Qn = 1 & Q'n = 0), then S = 1 and R = 0. Since S = 1 and R = 0, the basic flip-flop changes its state and resets.

Case 3: When the clock is applied and J = 1 and K = 0 and the previous state of the flip-flop is reset (i.e., Qn = 0 and Q'n = 1), then S = 0 and R = 1. Since S = 0 and R = 1, the basic flip-flop changes its state and goes to the set state. But if the flip-flop is already in set condition (i.e., Qn = 1 and Q'n = 0), then S = 1 and R = 1. Since S = 1 and R = 1, the basic flip-flop does not alter its state and remains in the set state.

Case 4: When the clock is applied and J = 1 and K = 1 and the previous state of the flip-flop is reset (i.e., Qn = 0 and Q'n = 1), then S = 0 and R = 1. Since S = 0 and R = 1, the basic flip-flop changes its state and goes to the set state. But if the flip-flop is already in set condition (i.e., Qn = 1 and Q'n = 0), then S = 1 and R = 0. Since S = 1 and R = 0, the basic flip-flop changes its state and goes to the reset state. So we find that for J = 1 and K = 1, the flip-flop toggles its state from set to reset and vice versa.

Must Read Shift Registers in Digital Electronics