Introduction

In computer architecture and system design, optimizing memory access and throughput stands as a fundamental objective. One notable technique that addresses this concern is memory interleaving. Memory interleaving operates at the core of modern computing systems, enhancing memory bandwidth and overall system performance.

As a result, we may claim that interleave memory honors all memory requests regardless of the status of the other modules. Main memory (random-access memory, RAM) often comprises a collection of DRAM memory chips grouped to form a memory bank. With a memory controller that supports interleaving, these memory banks can then be laid out, so that's why they are interleaved.

(Also, see Different Types of RAM)

This article will help you understand memory interleaving.

So let us begin to understand memory interleaving in depth.

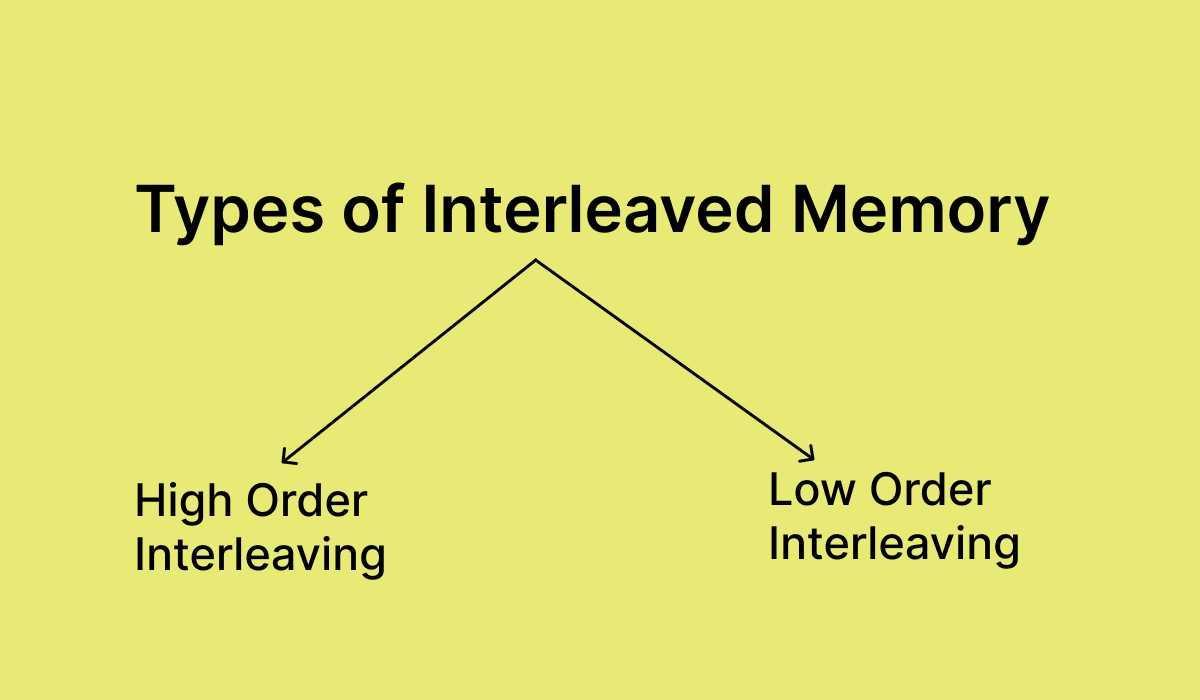

What is Interleaved Memory?

Main memory (random-access memory, RAM) is often made up of a collection of DRAM memory chips, with several chips grouped to form a memory bank. The memory banks can then be laid out to interleave using a memory controller that supports interleaving.

In turn, interleaved memory addresses are assigned to each memory bank. In a system with two interleaved memory banks (assuming word-addressable memory), for example, if logical address 32 belongs to bank 0, logical address 33 belongs to bank 1, logical address 34 belongs to bank 0, and so on. When there are n banks and a memory location ( i sits in bank i mod n. ), The memory is said to be n-way interleaved.

For example, if we have four memory banks (four-way interleaved memory), each with 256 bytes, the Block Oriented method (no interleaving) will allocate An instruction pipeline that can request both instructions and operands from the main memory at the same time, which is not possible with regular memory access.

Similarly, an arithmetic pipeline necessitates the simultaneous retrieval of two operands from the main memory. The first bank has virtual addresses ranging from 0 to 255, whereas the second bank has addresses ranging from 256 to 511. However, in Interleaved memory, virtual address 0 corresponds to the first memory bank, virtual address 1 corresponds to the second memory bank, virtual address 2 corresponds to the third memory bank, virtual address 3 corresponds to the fourth memory bank, and virtual address 4 corresponds to the first memory bank again.

As a result, the CPU can access different parts without waiting for memory to be cached. Several memory banks supply data in turn.

Memory interleaving is a memory speed-up technique. It is a procedure that improves the system's efficiency, speed, and dependability.