Introduction

RISC stands for Reduced Instruction Set Computer Processor, and CISC stands for Complex Instruction Set Computer Processor, both are used to increase CPU performance.

RISC reduces the cycles per instruction at the cost of the number of instructions per program.

CISC tries to minimize the number of instructions per program but at the cost of increasing the number of cycles per instruction.

A few decades earlier, when the programming was done using assembly language, a need was felt to make instruction do more tasks because programming in assembly was tedious and error-prone; because of this, CISC architecture evolved but with the uprise of high-level language dependency on assembly reduced the RISC architecture prevailed.

Let’s understand both RISC and CISC concepts in-depth.

Recommended Topic, Microinstruction in Computer Architecture

What is Reduced Instruction Set Computer (RISC)?

RISC is a microprocessor architecture that uses a simple set of instructions that can be substantially modified. It is designed to reduce the time it takes for instructions to execute by optimizing and reducing the number of instructions. It means that each instruction cycle has only one clock per cycle, and each cycle consists of three parameters: fetch, decode, and execute. The RISC processor can also combine multiple complex instructions into a simple one. RISC chips require several transistors, making them less expensive to develop and reducing instruction execution time.

Examples of RISC processors are PowerPC, Microchip PIC, SUN's SPARC, RISC-V.

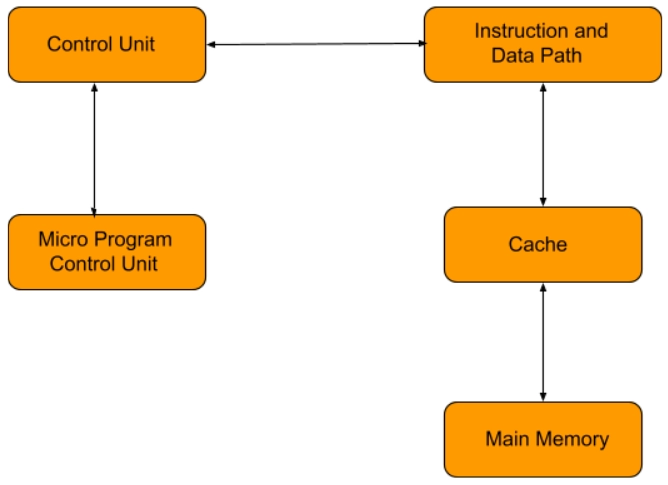

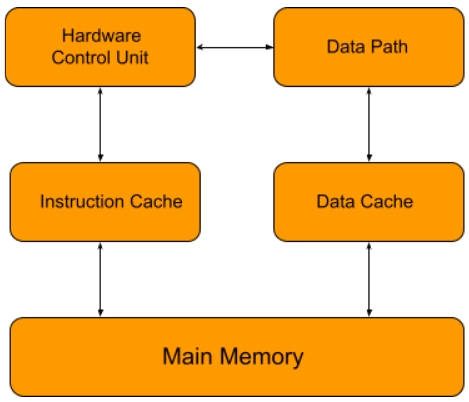

Architecture of RISC

RISC architecture is a computing paradigm that emphasizes simplicity and efficiency by using a smaller set of instructions with uniform execution times. It prioritizes performance optimization by streamlining instruction execution, minimizing complexity, and maximizing hardware utilization. RISC processors typically feature a simpler instruction set, fewer addressing modes, and a focus on pipelining and parallelism for faster execution. This architecture is prevalent in modern microprocessors, embedded systems, and high-performance computing environments due to its ability to deliver efficient, scalable, and cost-effective solutions.

RISC Processor of Features

Some of the crucial features of the RISC processor are:-

1.) RISC processors use one clock per cycle (CPI) to execute each instruction in a computer. Each CPI also comprises the methods for fetching, decoding, and executing computer instructions.

2.) Multiple registers in RISC processors allow them to hold instructions, reply fast to the computer, and interact with computer memory as little as possible.

3.) The RISC processors use the pipelining technique to execute multiple parts or stages of instructions to perform more efficiently.

4.) RISC has a simple addressing mode and fixed instruction length for the pipeline execution.

5.) It uses LOAD and STORE instruction to access the memory location.

Also See, Shift Registers in Digital Electronics and what is middleware

Characteristics of RISC

- Simplified Instruction Set: RISC architectures feature a reduced and simplified instruction set compared to Complex Instruction Set Computing (CISC) architectures.

- Uniform Instruction Format: Instructions in RISC architectures typically have a uniform length and format, simplifying decoding and execution.

- Single Clock Cycle Execution: Most instructions execute in a single clock cycle, leading to predictable and consistent performance.

- Register-based Operations: RISC architectures heavily rely on registers for operand storage and manipulation, reducing memory access overhead.

- Hardwired Control: Control logic in RISC processors is often hardwired, resulting in faster instruction decoding and execution.

- Pipelining: RISC architectures commonly employ pipelining techniques to overlap instruction execution stages, enhancing throughput.

- Highly Optimized for Compiler: RISC designs are optimized for compiler efficiency, enabling better code generation and optimization strategies.

Advantages of RISC

- Simplified instruction set facilitates faster decoding and execution.

- Uniform instruction format simplifies hardware design and instruction decoding.

- Single clock cycle execution ensures predictable and consistent performance.

- Register-based operations reduce memory access overhead and enhance performance.

- Hardwired control logic speeds up instruction decoding and execution.

- Pipelining techniques increase throughput and overall system performance.

- Optimized for compiler efficiency, enabling better code generation and optimization.

Disadvantages of RISC

- Limited flexibility due to a reduced instruction set.

- May require more instructions to perform complex operations compared to CISC architectures.

- Increased reliance on compiler optimization for performance.

- Reduced support for complex memory addressing modes.

- Less suitable for applications requiring extensive hardware support for specific tasks.

- Initial development and optimization may require more effort and resources.

- Compatibility issues may arise when porting legacy software from CISC architectures.